# LVDS Output with 600 mV to 1200 mV Output Swing

### Contents

| 1 | Introduction                                           | 1 |

|---|--------------------------------------------------------|---|

| 2 | LVDS Output Principles of Operation                    | 2 |

| 3 | Adjusting LVDS Differential Swing to 600 mV to 1200 mV | 3 |

# **1** Introduction

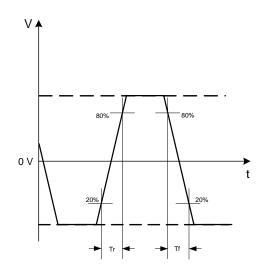

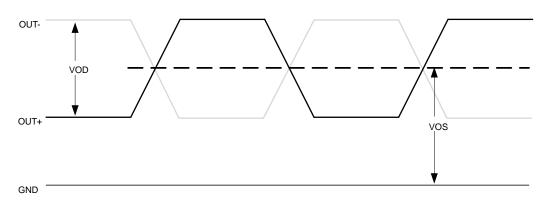

A reference clock output with a differential swing of 600 mV to 1200 mV as defined in Figure 1.1 below is becoming a common requirement for optical modules and is driven by the chipset input requirements. This definition of differential swing is defined as OUT+ minus OUT- and is how the differential receiver will process the waveform. The OUT+ minus OUT- subtraction effectively doubles the amplitude of waveform relative to an oscilloscope observation when measuring each of the differential outputs in single-ended mode as shown in Figure 1.2 on page 2 for example purposes. Because different differential output formats can have different definitions for differential waveform swing levels, it is very important to confirm the exact requirements with the chipset vendor, preferably with a waveform diagram.

This application note discusses use of the SiTime SiT9365/SiT9366 LVDS output to provide 600 mV to 1200 mV differential swing amplitude as defined in Figure 1.1 below.

Figure 1.1. Differential Waveform Definition

Figure 1.2. Differential Output – Single-Ended View

# 2 LVDS Output Principles of Operation

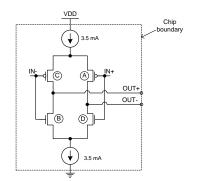

LVDS is a high-speed digital interface suitable for many applications that require low power consumption and high noise immunity. LVDS outputs use differential signals with low voltage swings to transmit data at high rates. on the following page shows the output structure of an LVDS driver, consisting of 3.5 mA nominal current sources connected to differential outputs via a switching network, sometimes referred to as "H" switch. The outputs are typically connecting to 100  $\Omega$  differential transmission lines terminated with a 100  $\Omega$  resistor across the receiver inputs. The resistor value matches the impedance of the transmission lines and provides a current path for the signal.

Figure 2.1. LVDS Driver Output Structure

The driver includes circuitry to set the common mode to 1.2 V nominally regardless of VDD. Therefore, there is no need for externally biasing the driver to any specific voltage. Also, an LVDS output can be connected to any LVDS input without any concern about actual supply voltage of the oscillator.

Signal switching is accomplished with four transistors labeled A, B, C, and D. Since the impedance of the receiver is typically high, virtually all current from the driver flows through the standard 100  $\Omega$  differential termination resistor, resulting in a voltage difference of 350 mV between the receiver inputs. In Figure 2.1, when the signal IN is low, transistors A and B are turned on; the current flows through the

transistor A and the 100  $\Omega$  resistor and returns through the transistor B. When the signal IN is high, transistors C and D are turned on; the current flows through the transistor C and the 100  $\Omega$  resistor and returns through the transistor D, resulting in -350 mV voltage across the receiver.

From the receiver's perspective, the direction of the current flowing through the termination resistor determines whether a positive or negative differential voltage is registered. A positive differential voltage represents a logic high level, while a negative differential voltage represents a logic low level.

# **3** Adjusting LVDS Differential Swing to 600 mV to 1200 mV

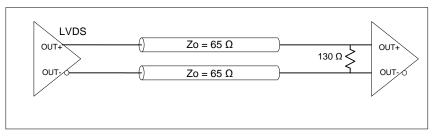

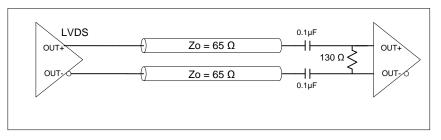

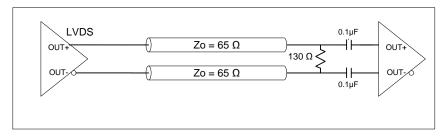

Differential output swing of SiTime oscillators with LVDS output and standard 100  $\Omega$  termination is 700 mV typical with 500 mV to 900 mV minimum-to-maximum window. To adjust the differential LVDS swing to the 600 mV to 1200 mV range, SiTime recommends a termination resistor value of 130  $\Omega$  as shown in figure 3.0 below. It will move typical output swing value to 910 mV and minimum-to-maximum range to 650 mV to 1170 mV. To get full impedance matching of the transmission line and termination resistor, it is recommended to increase line impedance to 65  $\Omega$ .

If an LVDS driver and receiver are operating with different common mode voltages, an AC termination is recommended. A capacitor is used to block the DC current path from the driver, so the receiver must implement its own input bias circuit. AC coupling termination circuit is shown at Figure 3.1 and Figure 3.2. As shown on these termination diagrams, the AC-coupling capacitors can be placed before or after the load termination resistor.

Figure 3.1. LVDS Single AC Termination at the Load

Figure 3.2. LVDS Single AC Termination at the Load

Figure 3.3. LVDS Single AC Termination at the Load

### SiTime Corporation, 5451 Patrick Henry Drive, Santa Clara, CA 95054, USA | Phone: +1-408-328-4400 | Fax: +1-408-328-4439

© SiTime Corporation, July 2019. The information contained herein is subject to change at any time without notice. SiTime assumes no responsibility or liability for any loss, damage or defect of a Product which is caused in whole or in part by (i) use of any circuitry other than circuitry embodied in a SiTime product, (ii) misuse or abuse including static discharge, neglect or accident, (iii) unauthorized modification or repairs which have been soldered or altered during assembly and are not capable of being tested by SiTime under its normal test conditions, or (iv) improper installation, storage, handling, warehousing or transportation, or (v) being subjected to unusual physical, thermal, or electrical stress.

Disclaimer: SiTime makes no warranty of any kind, express or implied, with regard to this material, and specifically disclaims any and all express or implied warranties, either in fact or by operation of law, statutory or otherwise, including the implied warranties of merchantability and fitness for use or a particular purpose, and any implied warranty arising from course of dealing or usage of trade, as well as any common-law duties relating to accuracy or lack of negligence, with respect to this material, any SiTime product and any product documentation. Products sold by SiTime are not suitable or intended to be used in a life support application or component, to operate nuclear facilities, or in other mission critical applications where human life may be involved or at stake. All sales are made conditioned upon compliance with the critical uses policy set forth below.

#### CRITICAL USE EXCLUSION POLICY

BUYER AGREES NOT TO USE SITIME'S PRODUCTS FOR ANY APPLICATION OR IN ANY COMPONENTS USED IN LIFE SUPPORT DEVICES OR TO OPERATE NUCLEAR FACILITIES OR FOR USE IN OTHER MISSION-CRITICAL APPLICATIONS OR COMPONENTS WHERE HUMAN LIFE OR PROPERTY MAY BE AT STAKE.

SiTime owns all rights, title and interest to the intellectual property related to SiTime's products, including any software, firmware, copyright, patent, or trademark. The sale of SiTime products does not convey or imply any license under patent or other rights. SiTime retains the copyright and trademark rights in all documents, catalogs and plans supplied pursuant to or ancillary to the sale of products over services by SiTime. Unless otherwise agreed to in writing by SiTime, any reproduction, modification, translation, compliation, or representation of this material shall be strictly prohibited.