| Title: | Performance report for SiT5156, 20 MHz, LVCMOS |       |               |

|--------|------------------------------------------------|-------|---------------|

| Type:  | Performance report                             | Rev:  | 1.2           |

| Orig:  |                                                | Date: | July 17, 2018 |

### Performance report for SiT5156 - 20 MHz, LVCMOS

#### Data:

- Frequency stability over temperature

- Frequency slope

- Frequency hysteresis over temperature

- Allan Deviation

- MTIE

- TDEV

- Phase noise

- Output frequency power supply sensitivity

- Output frequency load sensitivity

- Output waveforms

- Pull range linearity

- Random Phase jitter, Period jitter, Duty cycle, Rise/Fall time, Amplitude, Current consumption

| Title: | Performance report for SiT5156, 20 MHz, LVCMOS |       |               |

|--------|------------------------------------------------|-------|---------------|

| Type:  | Performance report                             | Rev:  | 1.2           |

| Orig:  |                                                | Date: | July 17, 2018 |

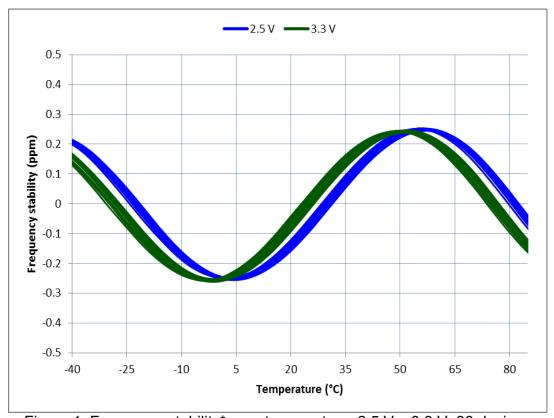

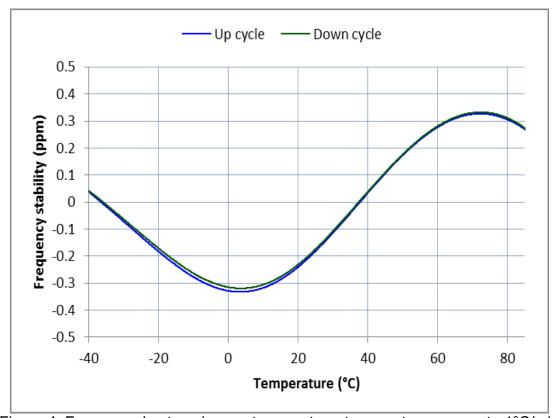

Figure 1: Frequency stability\* over temperature, 2.5 V – 3.3 V, 30 devices

\*SiT5156 frequency stability is independent of output frequency.

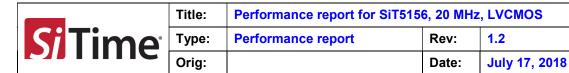

Figure 2: Frequency versus temperature slope, 30 devices

| Title: | Performance report for SiT5156, 20 MHz, LVCMOS |       |               |

|--------|------------------------------------------------|-------|---------------|

| Type:  | Performance report                             | Rev:  | 1.2           |

| Orig:  |                                                | Date: | July 17, 2018 |

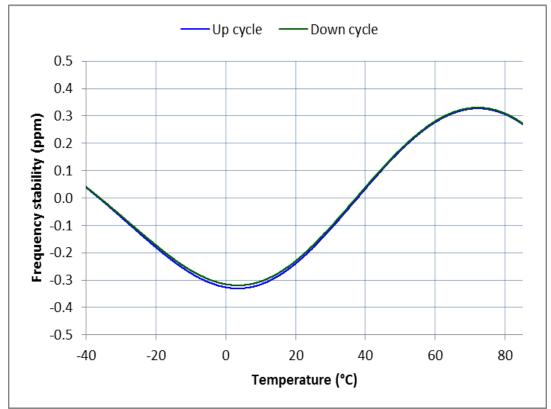

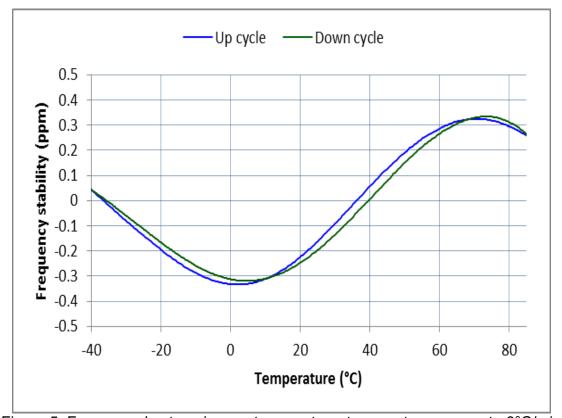

Figure 3: Frequency hysteresis over temperature, temperature ramp rate 0.5°C/min

| Title: | Performance report for SiT5156, 20 MHz, LVCMOS |       |               |

|--------|------------------------------------------------|-------|---------------|

| Type:  | Performance report                             | Rev:  | 1.2           |

| Orig:  |                                                | Date: | July 17, 2018 |

Figure 4: Frequency hysteresis over temperature, temperature ramp rate 1°C/min

| Title: | Performance report for SiT5156, 20 MHz, LVCMOS |       |               |

|--------|------------------------------------------------|-------|---------------|

| Type:  | Performance report                             | Rev:  | 1.2           |

| Orig:  |                                                | Date: | July 17, 2018 |

Figure 5: Frequency hysteresis over temperature, temperature ramp rate 8°C/min

| Title: | Performance report for SiT5156, 20 MHz, LVCMOS |       |               |

|--------|------------------------------------------------|-------|---------------|

| Type:  | Performance report                             | Rev:  | 1.2           |

| Orig:  |                                                | Date: | July 17, 2018 |

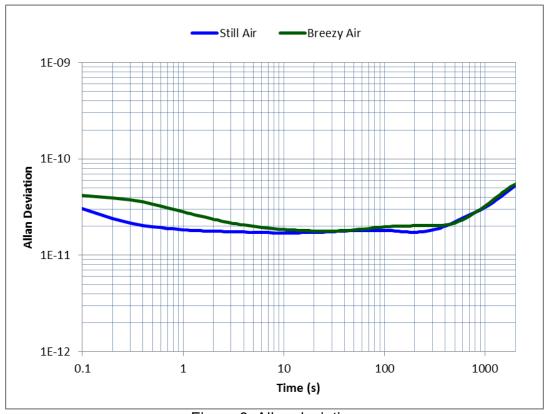

Figure 6: Allan deviation

Table 1: Allan deviation

| Time (s)   | 0.1      | 1        | 10       | 100      | 1000     |

|------------|----------|----------|----------|----------|----------|

| Still Air  | 3.04E-11 | 1.84E-11 | 1.71E-11 | 1.81E-11 | 3.16E-11 |

| Breezy Air | 4.17E-11 | 2.82E-11 | 1.85E-11 | 1.98E-11 | 3.26E-11 |

| Title: | Performance report for SiT5156, 20 MHz, LVCMOS |       |               |

|--------|------------------------------------------------|-------|---------------|

| Type:  | Performance report                             | Rev:  | 1.2           |

| Orig:  |                                                | Date: | July 17, 2018 |

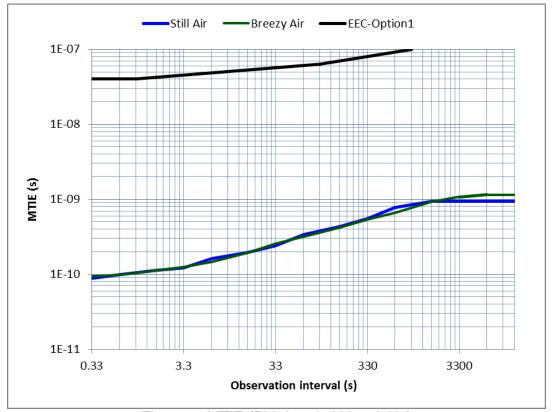

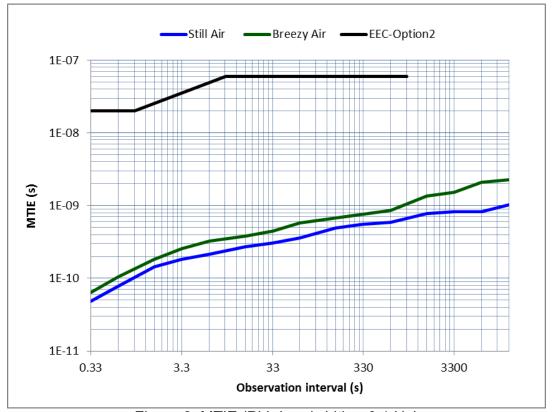

Figere 7: MTIE (PLL bandwidth = 3 Hz)

| Title: | Performance report for SiT5156, 20 MHz, LVCMOS |       |               |

|--------|------------------------------------------------|-------|---------------|

| Type:  | Performance report                             | Rev:  | 1.2           |

| Orig:  |                                                | Date: | July 17, 2018 |

Figure 8: MTIE (PLL bandwidth = 0.1 Hz)

| Title: | Performance report for SiT5156, 20 MHz, LVCMOS |       |               |

|--------|------------------------------------------------|-------|---------------|

| Type:  | Performance report                             | Rev:  | 1.2           |

| Orig:  |                                                | Date: | July 17, 2018 |

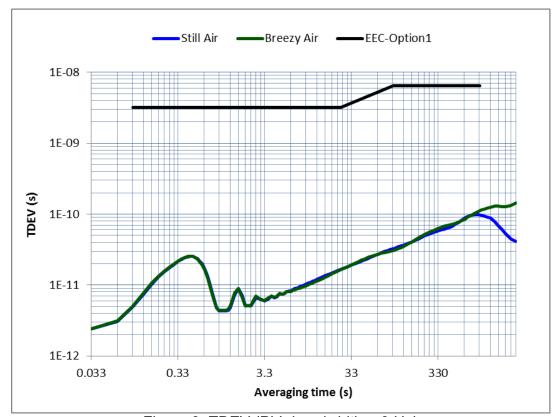

Figure 9: TDEV (PLL bandwidth = 3 Hz)

| Title: | Performance report for SiT5156, 20 MHz, LVCMOS |       |               |

|--------|------------------------------------------------|-------|---------------|

| Type:  | Performance report                             | Rev:  | 1.2           |

| Orig:  |                                                | Date: | July 17, 2018 |

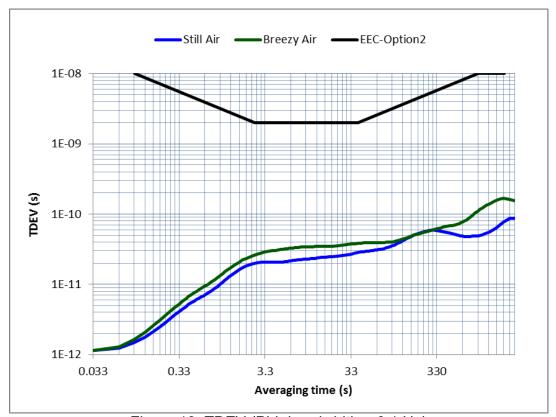

Figure 10: TDEV (PLL bandwidth = 0.1 Hz)

| Title: | Performance report for SiT5156, 20 MHz, LVCMOS |       |               |

|--------|------------------------------------------------|-------|---------------|

| Type:  | Performance report                             | Rev:  | 1.2           |

| Orig:  |                                                | Date: | July 17, 2018 |

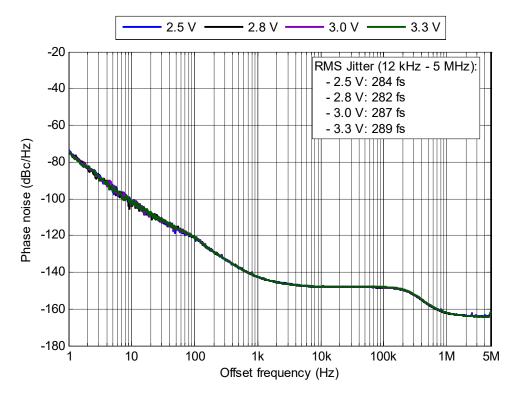

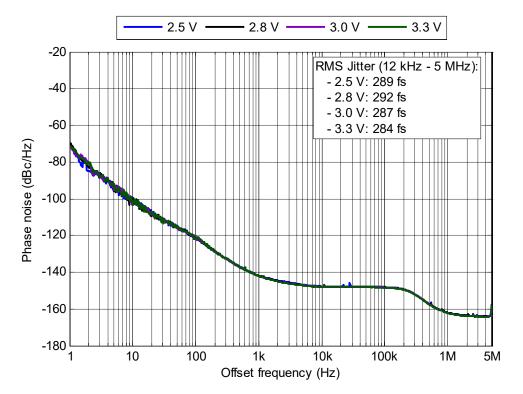

Figure 11: Phase noise TCXO/DCTCXO, 2.5 V - 3.3 V

Table 2: Phase noise TCXO/DCTCXO

| Voltage | Phase noise (dBc/Hz) |        |        |        |        |         |        |        |

|---------|----------------------|--------|--------|--------|--------|---------|--------|--------|

| Voltage | 1 Hz                 | 10 Hz  | 100 Hz | 1 KHz  | 10 KHz | 100 KHz | 1 MHz  | 5 MHz  |

| 2.5 V   | -73.3                | -101.9 | -121.6 | -142.4 | -147.9 | -148.4  | -162.2 | -162.9 |

| 2.8 V   | -74.3                | -102.1 | -120.9 | -142.5 | -148.0 | -148.4  | -162.3 | -162.8 |

| 3.0 V   | -73.9                | -102.3 | -120.8 | -142.6 | -148.0 | -148.3  | -162.1 | -164.0 |

| 3.3 V   | -73.8                | -102.6 | -120.8 | -142.4 | -147.9 | -148.2  | -162.1 | -163.3 |

| Title: | Performance report for SiT5156, 20 MHz, LVCMOS |       |               |  |  |

|--------|------------------------------------------------|-------|---------------|--|--|

| Type:  | Performance report                             | Rev:  | 1.2           |  |  |

| Orig:  |                                                | Date: | July 17, 2018 |  |  |

Figure 12: Phase noise VCTCXO, 2.5 V - 3.3 V

Table 3: Phase noise VCTCXO

| Voltage | Phase noise (dBc/Hz) |        |        |        |        |         |        |        |

|---------|----------------------|--------|--------|--------|--------|---------|--------|--------|

| voltage | 1 Hz                 | 10 Hz  | 100 Hz | 1 KHz  | 10 KHz | 100 KHz | 1 MHz  | 5 MHz  |

| 2.5 V   | -70.9                | -99.3  | -121.4 | -141.7 | -147.8 | -148.3  | -162.1 | -158.4 |

| 2.8 V   | -69.4                | -100.2 | -121.0 | -142.2 | -147.8 | -148.2  | -162.0 | -157.2 |

| 3.0 V   | -71.3                | -101.4 | -120.6 | -142.4 | -147.9 | -148.2  | -162.3 | -157.9 |

| 3.3 V   | -70.5                | -101.4 | -120.8 | -141.9 | -148.0 | -148.4  | -162.3 | -158.2 |

| Title: | Performance report for SiT5156, 20 MHz, LVCMOS |       |               |  |  |

|--------|------------------------------------------------|-------|---------------|--|--|

| Type:  | Performance report                             | Rev:  | 1.2           |  |  |

| Orig:  |                                                | Date: | July 17, 2018 |  |  |

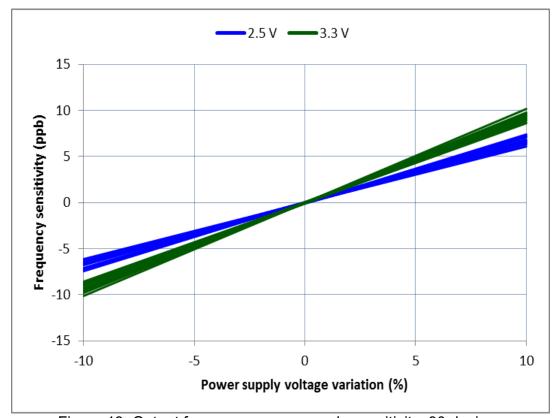

Figure 13: Output frequency power supply sensitivity, 30 devices

| Title: | Performance report for SiT5156, 20 MHz, LVCMOS |       |               |  |  |

|--------|------------------------------------------------|-------|---------------|--|--|

| Type:  | Performance report                             | Rev:  | 1.2           |  |  |

| Orig:  |                                                | Date: | July 17, 2018 |  |  |

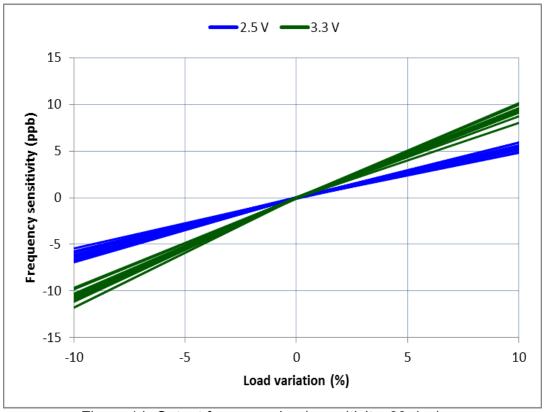

Figure 14: Output frequency load sensitivity, 30 devices

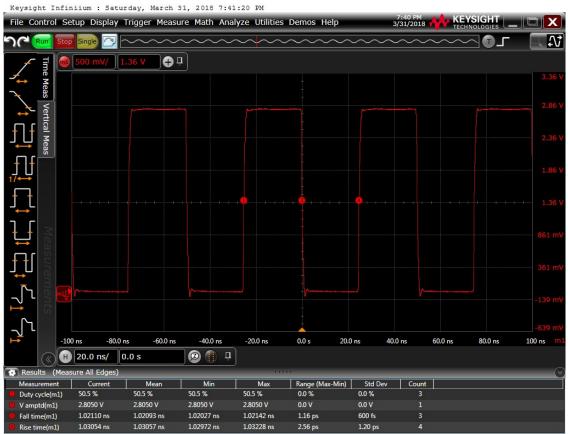

Figure 15: Output waveform, 2.5 V

Figure 16: Output waveform, 2.8 V

| Title: | Performance report for SiT5156, 20 MHz, LVCMOS |       |               |  |  |

|--------|------------------------------------------------|-------|---------------|--|--|

| Type:  | Performance report                             | Rev:  | 1.2           |  |  |

| Orig:  |                                                | Date: | July 17, 2018 |  |  |

Figure 17: Output waveform, 3.0 V

| Title: | Performance report for SiT5156, 20 MHz, LVCMOS |       |               |  |

|--------|------------------------------------------------|-------|---------------|--|

| Type:  | Performance report                             | Rev:  | 1.2           |  |

| Orig:  |                                                | Date: | July 17, 2018 |  |

Figure 18: Output waveform, 3.3 V

| Title: | Performance report for SiT5156, 20 MHz, LVCMOS |       |               |  |  |

|--------|------------------------------------------------|-------|---------------|--|--|

| Type:  | Performance report                             | Rev:  | 1.2           |  |  |

| Orig:  |                                                | Date: | July 17, 2018 |  |  |

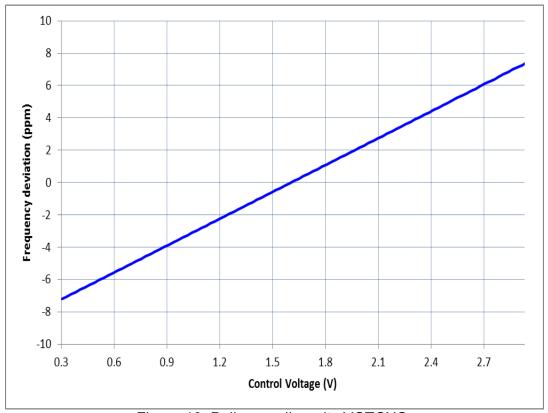

Figure 19: Pull range linearity VCTCXO.

<sup>\*</sup>Referred to the output frequency for control voltage equal to VDD/2

| Title: | Performance report for SiT5156, 20 MHz, LVCMOS |       |               |  |  |

|--------|------------------------------------------------|-------|---------------|--|--|

| Type:  | Performance report                             | Rev:  | 1.2           |  |  |

| Orig:  |                                                | Date: | July 17, 2018 |  |  |

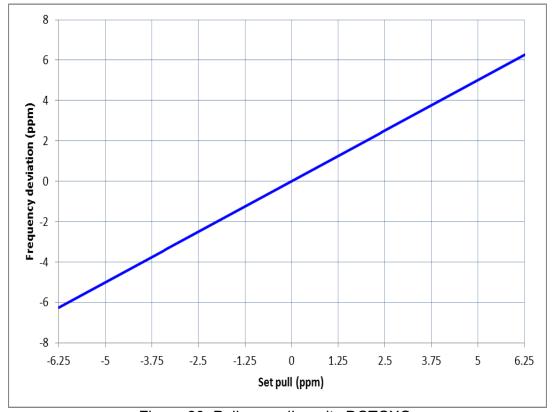

Figure 20: Pull range linearity DCTCXO.

\*Referred to the output frequency for frequency control value equal to 0

Table 4: Summary performance data

| Parameter                                            | Units     | Voltage |       |       |       |  |

|------------------------------------------------------|-----------|---------|-------|-------|-------|--|

| rai ailletei                                         | UTIILS    | 2.5 V   | 2.8 V | 3.0 V | 3.3 V |  |

| TCXO/DCTCXO Integrated Phase jitter (12 kHz - 5 MHz) | fs, rms   | 284     | 282   | 287   | 289   |  |

| VCTCXO Integrated Phase jitter (12 kHz - 5 MHz)      | fs, rms   | 289     | 292   | 287   | 284   |  |

| Period jitter                                        | ps, rms   | 1.12    | 0.00  | 0.00  | 1.01  |  |

| Period jitter (10,000 cycles)                        | ps, pk-pk | 7.99    | 0.00  | 0.00  | 8.12  |  |

| Duty cycle                                           | %         | 50.5    | 50.5  | 50.4  | 50.4  |  |

| Rise time (10% - 90%)                                | ps        | 1.06    | 1.03  | 1.09  | 0.98  |  |

| Fall time (90% - 10%)                                | ps        | 1.03    | 1.02  | 1.08  | 1.02  |  |

| Amplitude                                            | V         | 2.51    | 2.81  | 3.01  | 3.35  |  |

| Current consumption TCXO (no load)                   | mA        | 44.0    | 44.0  | 44.1  | 44.3  |  |

| Current consumption VCTCXO (no load)                 | mA        | 47.5    | 47.6  | 47.6  | 47.8  |  |

| Current consumption DCTCXO (no load)                 | mA        | 44.4    | 44.6  | 44.6  | 44.8  |  |

### **Conditions:**

- Frequency: 20 MHz

- VDD: 2.5 V, 2.8 V, 3.0 V, 3.3 V

Pull range: ±6.25 ppmTemperature: 25 °C

# **Equipment:**

| Model                        | Measurement / Purpose                            |

|------------------------------|--------------------------------------------------|

| Keysight DSA90604A (6 GHz,   | Period jitter, output amplitude, rise/fall time, |

| 20 Gsps)                     | duty cycle                                       |

| Keysight 5052B Signal Source | Phase noise, integrated phase jitter             |

| Analyzer                     |                                                  |

| Keysight 34980A              | Power supply current                             |

| Keysight E3631A              | Power supply                                     |

| Keysight 53230A              | Frequency                                        |

# Test setup:

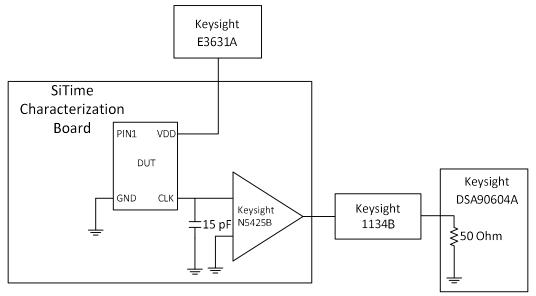

For waveform parameters measurement (rise/fall time, amplitude, duty cycle), DUT output is loaded with 15 pF. Output signal is measured using Keysight 1134B active probe with Keysight N5425B probe head. Figure 21 shows test setup diagram for waveform parameters measurement.

| 5451 Patrick Henry Drive, Santa Clara, California 95054 • 408.328.4400 • sitime.com | Page 22 of 25 |  |

|-------------------------------------------------------------------------------------|---------------|--|

|                                                                                     | i             |  |

Figure 21: Test setup for measuring waveform parameters (rise/fall time, amplitude, duty cycle)

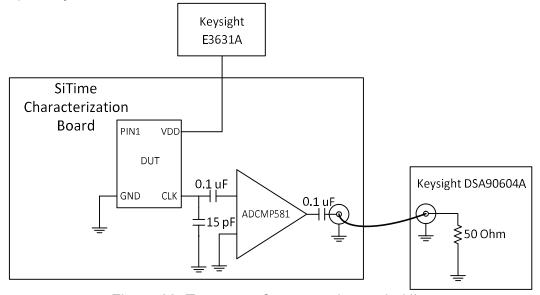

For period jitter measurement output is loaded with 15 pF. Jitter is measured from the output of hi-speed comparator (ADCMP581). AC coupled comparator's output is connected to oscilloscope channel. Figure 22 shows test setup diagram for period jitter measurement.

Figure 22: Test setup for measuring period jitter

| <b>Si</b> Time |       | Performance report for SiT5156, 20 MHz, LVCMOS |       |               |

|----------------|-------|------------------------------------------------|-------|---------------|

|                | Type: | Performance report                             | Rev:  | 1.2           |

|                | Orig: |                                                | Date: | July 17, 2018 |

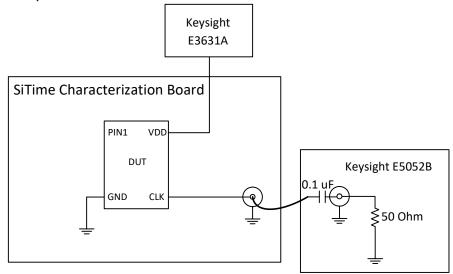

For phase noise measurements output is connected to 50  $\Omega$  measurement instrument input through AC coupling capacitor. Figure 23 shows test setup diagram for phase noise measurement.

Figure 23: Test setup for measuring phase noise

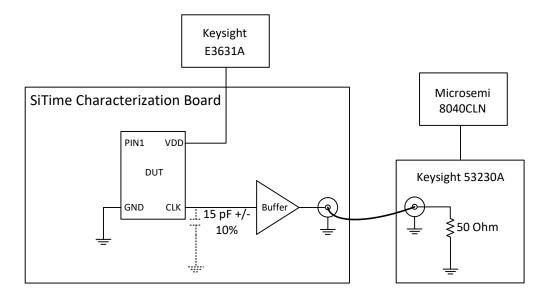

For frequency measurement (stability over temperature, frequency hysteresis, stability over voltage, stability over load, ADEV) buffered device output is connected to  $50~\Omega$  measurement instrument input (see figure 24).

Figure 24: Test setup for measuring frequency

| Si Time | Title: | Performance report for SiT5156, 20 MHz, LVCMOS |       |               |  |

|---------|--------|------------------------------------------------|-------|---------------|--|

|         | Type:  | Performance report                             | Rev:  | 1.2           |  |

|         | Orig:  |                                                | Date: | July 17, 2018 |  |

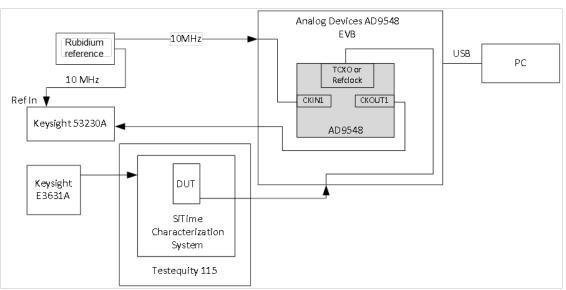

For wander (MTIE, TDEV) measurement AD9548 DPLL is used. DPLL is referenced from rubidium frequency reference. SiTime Super-TCXO is used as system clock for DPLL programmed to different bandwidths. Frequency is measured continuously (gap free mode) with 33 ms gate time. Figure 25 shows setup diagram for wander measurements.

Figure 25: Test setup for measuring wander