Six industry standard footprints as small as 5.0 x 3.2 mm

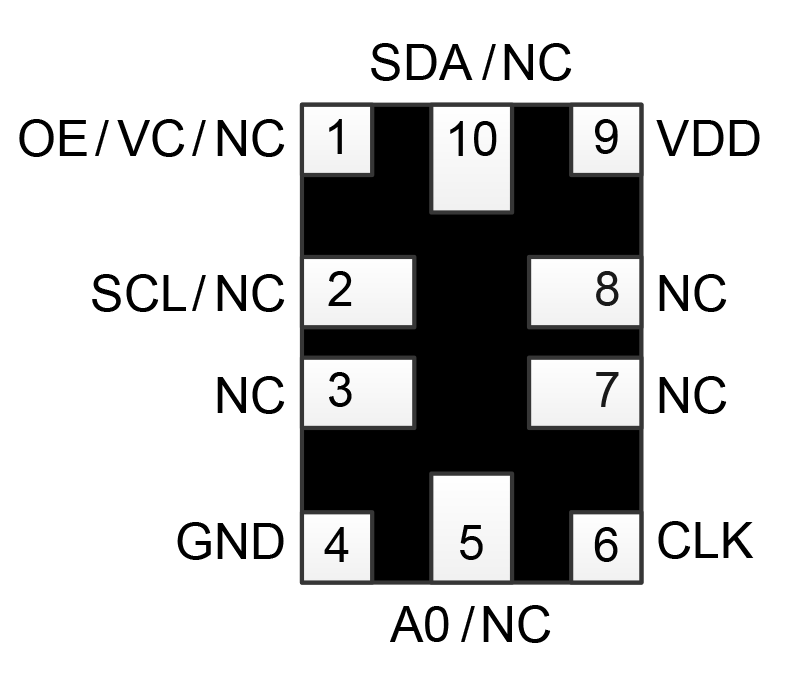

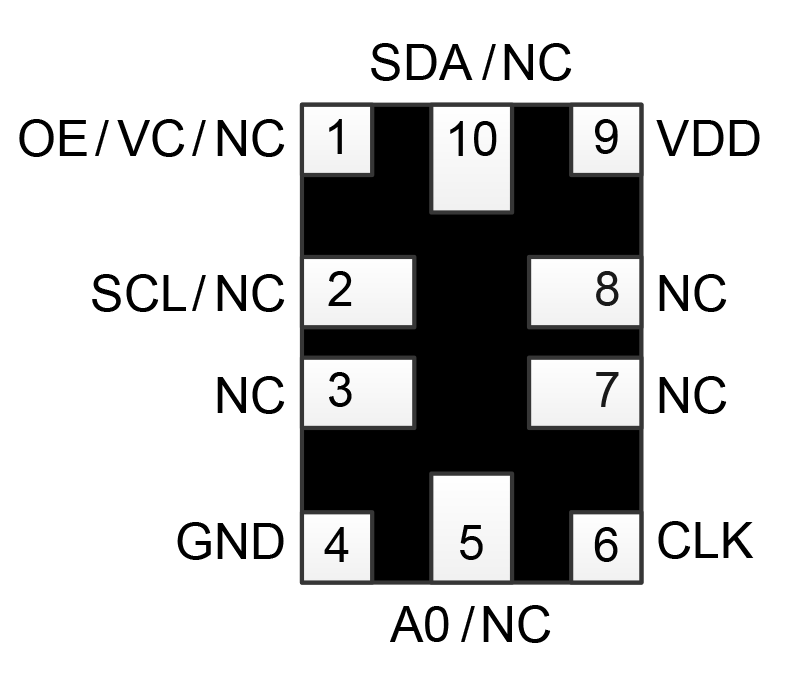

坐5155 pin assignments

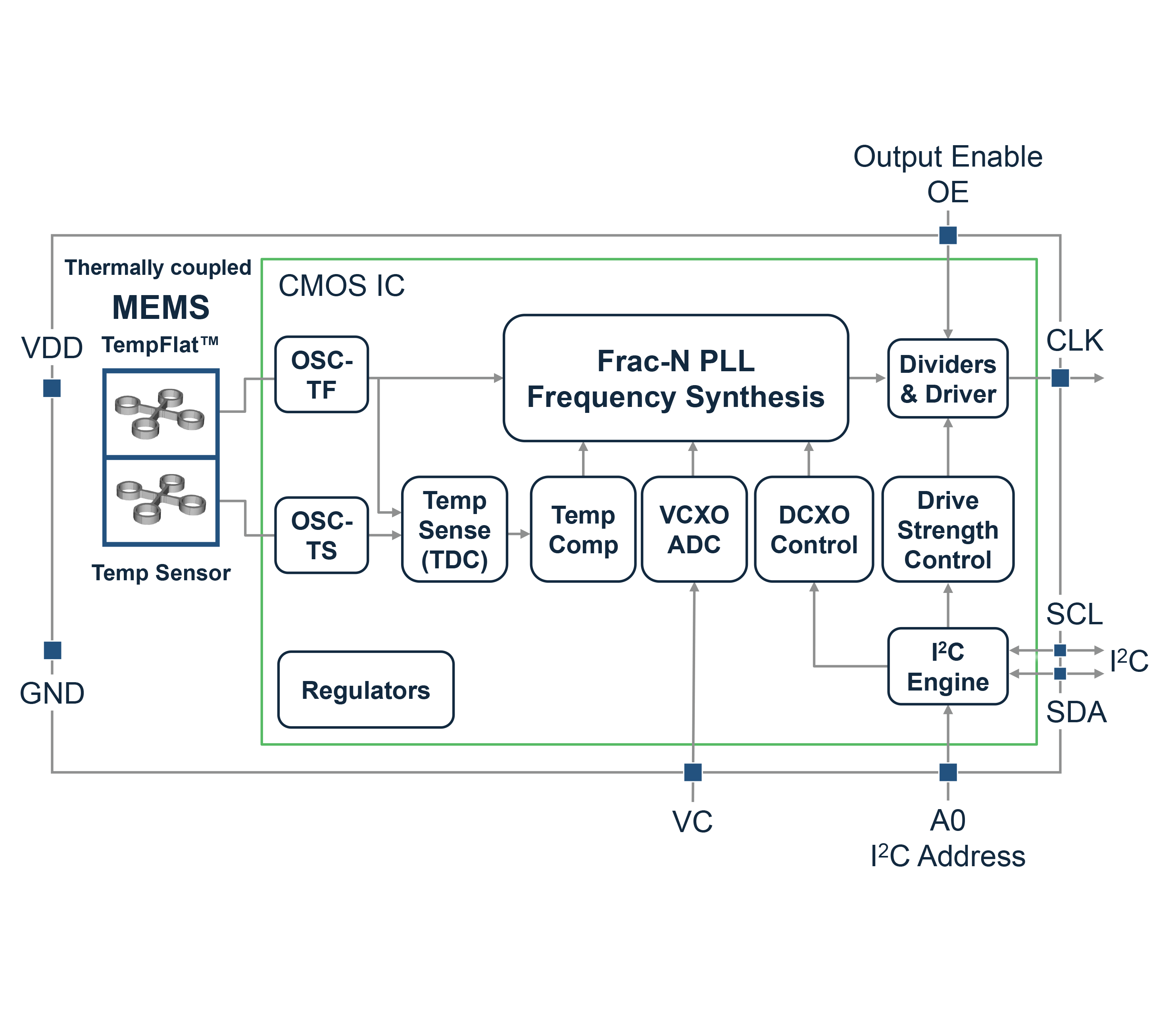

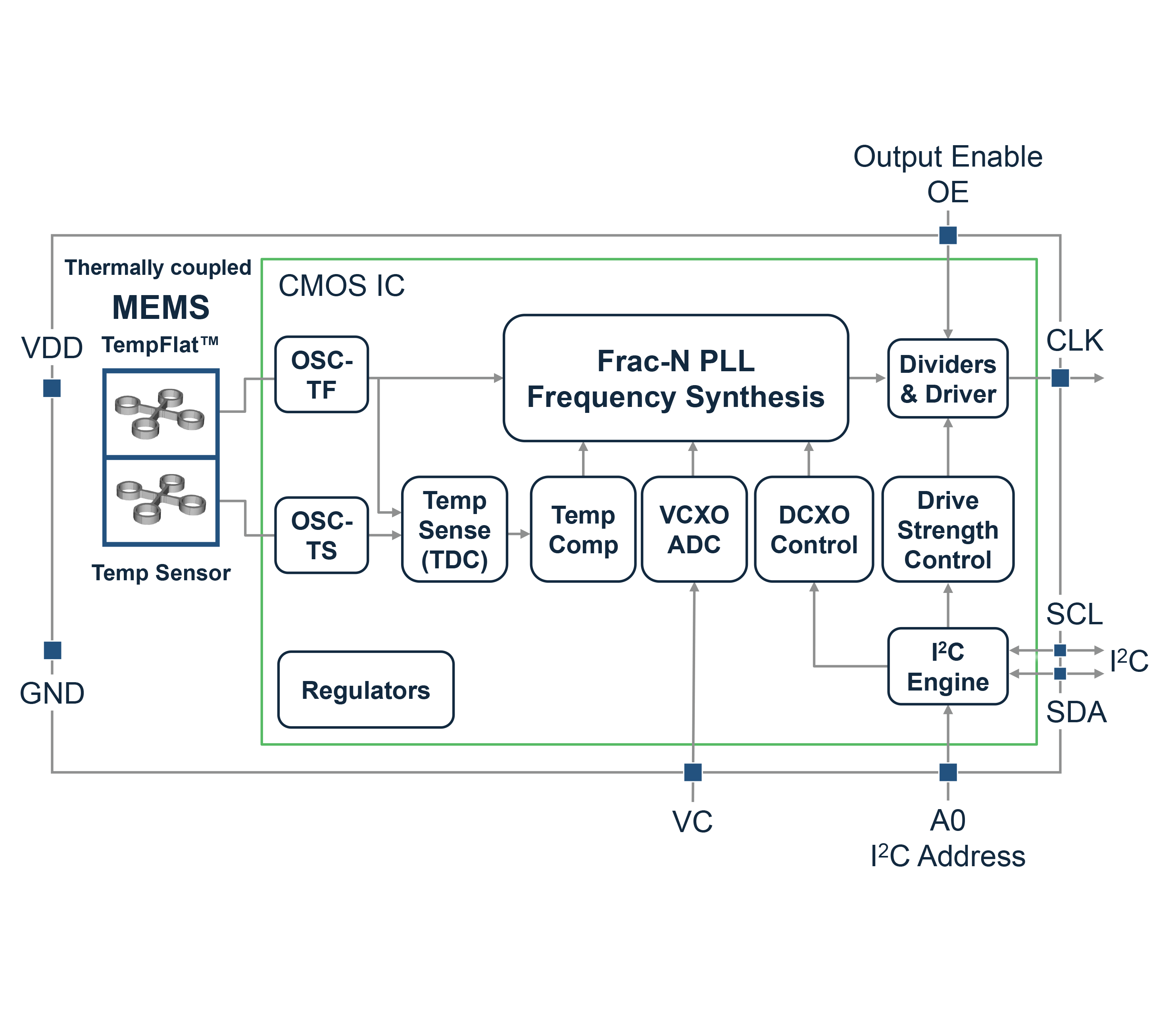

坐5155 block diagram

Exceptional dynamic stability under airflow, fast temp. ramp

- ±500 ppb过度。稳定

- 3E-11 ADEV在10秒平均时间

- ±15 ppb/°C frequency slope (ΔF/ΔT), 10 °C/min ramp

- Enables fastest satellite lock under any operating conditions

20x better phase noise under vibration

在高振动环境中最小化卫星锁的损失

No activity dips or micro jumps

- 消除了对昂贵的筛选或烧坏测试的需求

0.2 PS / MV电源噪声抑制(PSNR)

- Reduces BOM by eliminating a dedicated LDO for the TCXO

LVCMOS或剪裁SINEWAVE输出

- Optimize for best balance between EMI and jitter

Digital frequency tuning through I2C

- Eliminate frequency shift caused by board noise

Superior reliability

- 10亿小时MTBF

- Lifetime warranty

- Reduces repair costs and field failures due to clock components

- Industrial GNSS

- Telecom GNSS

- 精密GNSS.

- GPS / GNSS模块

- 坐5155 10.949297MHz LVCMOS

- 坐5155 10MHz LVCMOS

- SIT5155 16.368MHz LVCMOS.

- 坐5155 16.369MHz LVCMOS

- 坐5155 16.384MHz LVCMOS

- 坐5155 16.3676MHz LVCMOS

- SIT5155 16.367667MHz LVCMOS.

- SIT5155 20MHz LVCMOS.

- SIT5155 24.5535MHz LVCMOS.

- 坐5155 25MHz LVCMOS

- 坐5155 40MHz LVCMOS

- SIT5155 10.949297MHz夹剪弦波

- 坐5155 10MHz Clipped Sinewave

- SIT5155 16.368MHz夹在一起的SINEWAVE

- 坐5155 16.369MHz Clipped Sinewave

- SIT5155 16.384MHz剪裁SINEWAVE

- 坐5155 16.3676MHz Clipped Sinewave

- SIT5155 16.367667MHz剪切的正弦波

- 坐5155 20MHz Clipped Sinewave

- 坐5155 24.5535MHz Clipped Sinewave

- 坐5155 25MHz Clipped Sinewave

- 坐5155 40MHz Clipped Sinewave

坐6722 (5032) Evaluation Board User Manual– Evaluate oscillator performance

可靠性计算器– Get FIT/MTBF data for various operating conditions

Jitter Calculator and Plots– Convert phase noise to phase jitter, find phase noise plots

TimeMaster Configuration Software- 通过I2C / SP配置和评估振荡器

频率斜率(DF / DT)计算器– Calculate frequency slope over temperature

Time Error Simulation Software– Simulate and analyze the impact of the local oscillator

Ceramic 5032 10-Pins3D Step Model– Preview oscillator packages in 3D